# 2041 International Conference on Applied Mathematics, Modeling and Computer Simulation (AMMCS 2024) Low Power VLSI for Bio-Medical Application

Akarsha Ram<sup>1</sup>, Aakash  $M^1$ , Sivakumar  $R^{1*}$

<sup>1</sup>School of Electronics Engineering (SENSE), Vellore Institute of Technology, Vellore, India

\*Corresponding author's Email: rsivakumar@vit.ac.in

# Introduction

Cardiac Pacemakers are a set of implantable devices used to generate rhythm for slow beating hearts. The application requires the device to be miniature resulting in the implementation of a small battery as the power source. The project builds and simulates an amplifier present in the pacemaker and compares the adiabatic logic with CMOS to identify the power saving.

Keywords: Very Large Scale Integration, Adiabatic Circuits, Pacemaker, Area, Power Reduction, Simulation

# **Problem Statement and Objective**

• There is a gap in the implementation of the proposed adiabatic logic in the bio-medical field such as implantable devices.

• This project aims to bridge the gap between the theory of adiabatic logic in the bio-medical field through an adiabatic design and simulation of an Op-Amp used in Pace.

# Methodology

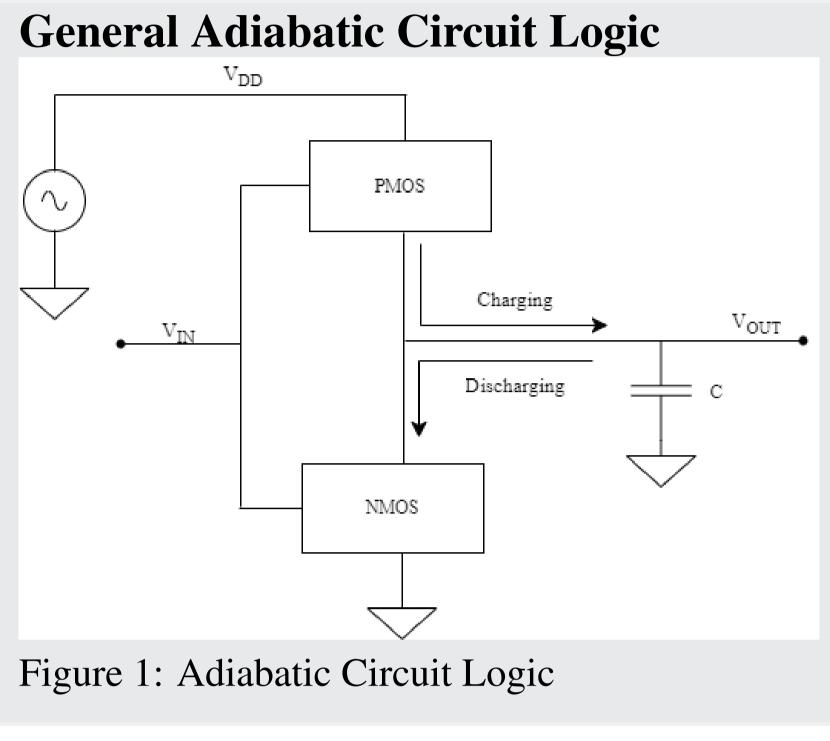

#### **Adiabatic Logic**

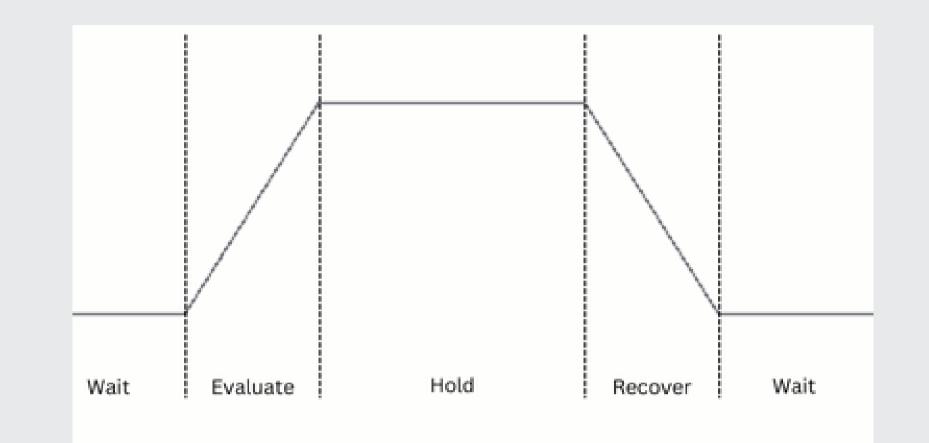

• Adiabatic circuits work on the principle of charging and discharging based on the clock cycle of the input voltage. The circuit charges power when the clock moves from low to high this phase is the Evaluate phase and discharges when the clock moves from high to low or the Recover phase.

• The logic can be implemented through capacitors or can be enhanced by the addition of CMOS inverters to the existing logic. There are many existing advanced adiabatic concepts such as Positive Feedback Adiabatic Logic (PFAL) and Efficient Charge Recovery Logic (ECRL)

#### **Operation of an Adiabatic System**

Figure 2: Supply Voltage Waveform of Adiabaic Cirucits

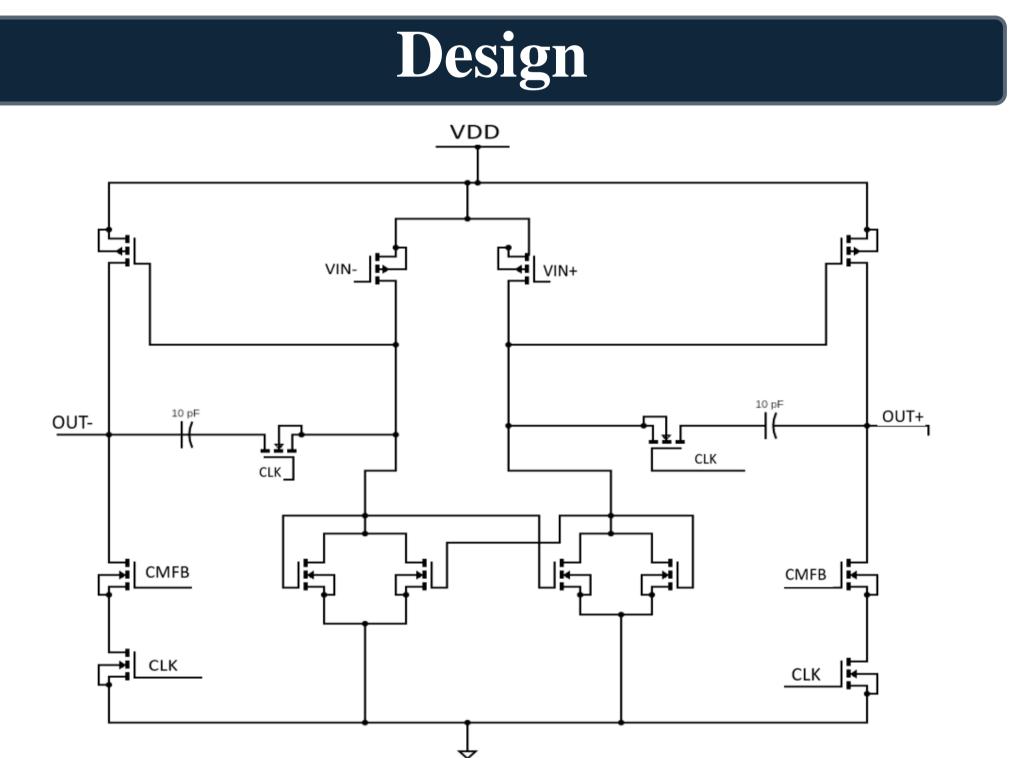

Figure 3: General Switched Op-Amp Circuit used in Pacemakers

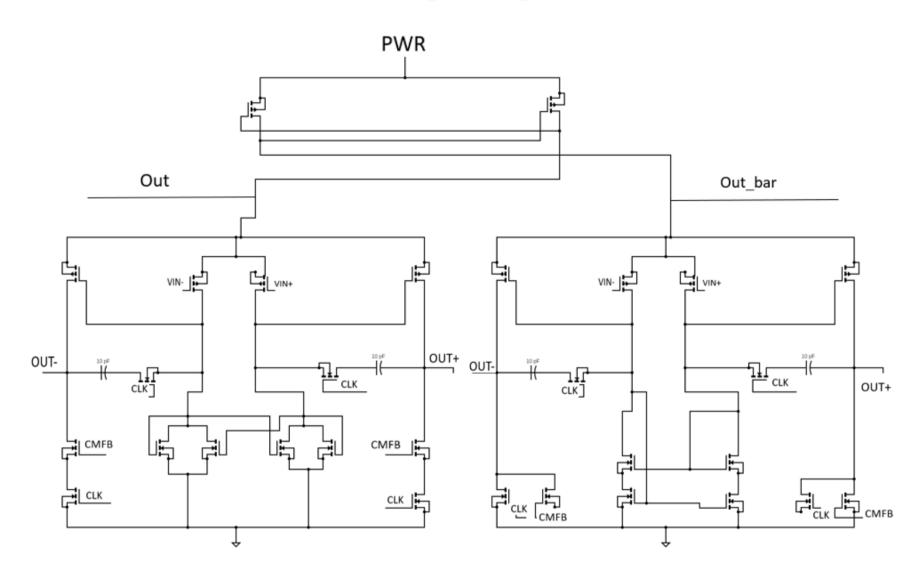

Figure 4: Switched Op-Amp using ECRL Adiabatic Logic

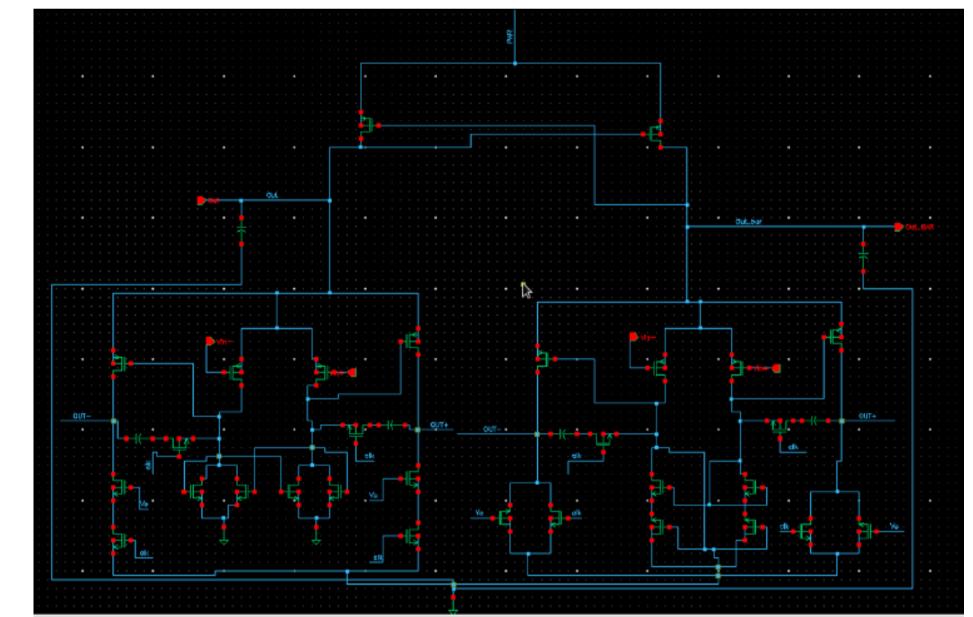

Figure 5: Adiabatic Op-Amp Implemented in Cadence Virtuoso

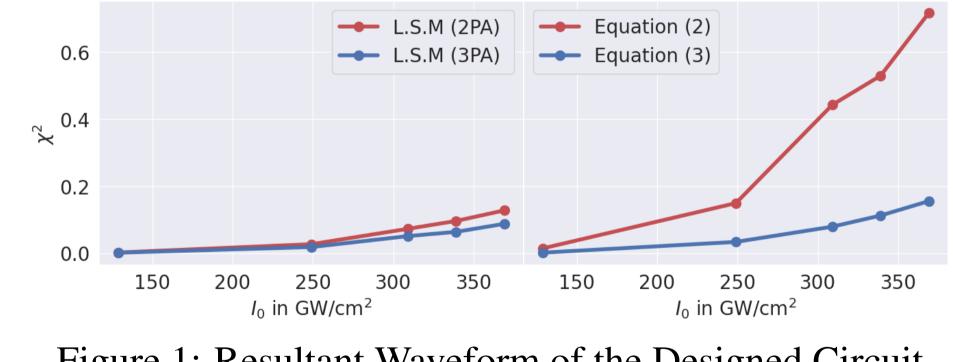

Figure 1: Resultant Waveform of the Designed Circuit

### **Results and Conclusion**

• The waveform obtained from the simulation matches the theoretical output showing the occurrence of evaluation and recovery

• The adiabatic method showed an 18% better efficiency than the conventional CMOS model.

• This implementation can be further developed by involving other parts of the pacemaker and performing a higher complexity implementation of the adiabatic logic.

### Acknowledgements

I would like to acknowledge the professors, staff, and the Electronics department of Vellore Institute of Technology for their constant support during this work.

### References

1. S. Garg and V. Niranjan, "A new Cascadable Adiabatic Logic Technique," Electrical and Electronics Engineering: An International Journal, vol. 5, no. 1, pp. 21-36, 2016

2. L. S. Y. Wong, S. Hossain, A. Ta, J. Edvinsson, D. H. Rivas and H. Naas, "A very low-power CMOS mixed-signal IC for implantable pacemaker applications," in IEEE Journal of Solid-State Circuits, vol. 39, no. 12, pp. 2446-2456, Dec. 2004, doi: 10.1109/JSSC.2004.837027.

3. Ishita Khindri, Kashika Hingorani, Vandana Niranjan. Low Power ALU using Wave Shaping Diode Adiabatic Logic. Indian Journal of VLSI Design Volume-2 Issue-2, September 2022. doi: https://doi.org/10.54105/ijvlsid.d1209.091422

4. Katre, S., Palsodkar, P., Ghute, M. (2012). Adiabatic Amplifier and Power Analysis of Different Adiabatic Inverters. In: Deep, K., Nagar, A., Pant, M., Bansal, J. (eds) Proceedings of the International Conference on Soft Computing for Problem Solving (SocProS 2011) December 20-22, 2011. Advances in Intelligent and Soft Computing, vol 130. Springer, India. https://doi.org/10.1007/978-81-322-0487-9-13